|

Project

Partners

News & Events

Publications

Related links

Legal notice

Private |

|

|

|  |

| Institut Mines-Telecom / Telecom SudParis

UMR5157 | |  |

The IT-TSP engineering school is associated to the National Centre of Scientific Research through a unity «Unité Mixte de Recherche (UMR 5157)» called « SAMOVAR».

This unity is composed of three teams with one dedicated to optical communications research.

It has a standing experience concerning optical characterisation of optical components under guiding conditions.

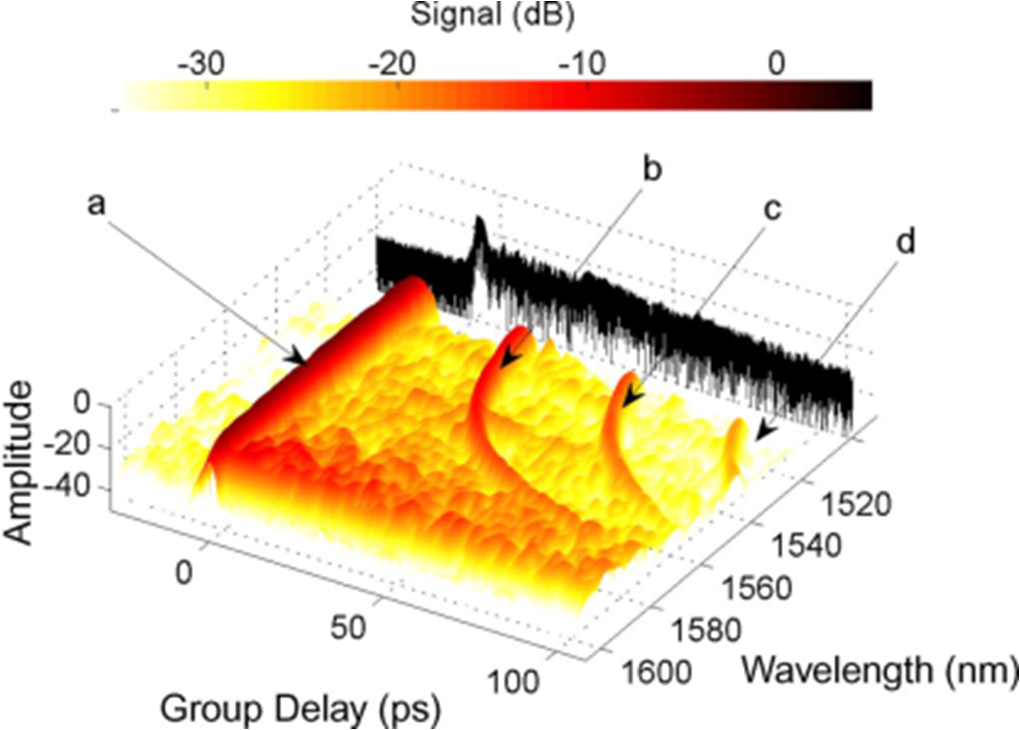

In particular, specific methods have been developed over the last ten years implying optical low-coherence reflectometry (OLCR) and component signature analysis.

These methods are based on IT-TSP proprietary simulations tools relying on versatile and adaptable electromagnetic models and standard BPM simulations.

In order to help the understanding of reflectometric signatures, optical and numerical treatments are purposely implemented to enhance some particularities of the optical devices or circuits under test

(performances, design, process, material quality, failure etc.).

A database of OLCR signatures of most of the optical telecom components already commercialised or still at an early stage of development is already constituted and exploitable.

| |  |

In the past, IT-TSP has been working in close collaboration with III-V lab concerning the characterisation of optical components.

It has also a national and international visibility (through national/international collaborations and projects).

The different reflectometry instruments developped by Telecom SudParis comprise phase sensitive setups such as Optical Coherence Interferometry, Optical Frequency Domain Interferopmetry, Optical Coherence Tomography.

These instruments enable scalable characterizations of photonic components and circuits with a complete (phase, spectrum, spatial and polarisation) recording of electromagnetic field reflected, transmitted

or scattered by the device under test, as needed during the early stage of conception of circuits for their optimization.

|